dr inż.

Jarosław Sugier

Zajęcia projektowe do przedmiotu „Układy cyfrowe i systemy wbudowane”

Zestawy Digilent S3E-Starter

Niniejsze opracowanie zawiera informacje pomocne w pracy nad projektami układów cyfrowych, które wykorzystują jako platformę sprzętową zestawy „S3EStarter Kit” firmy Digilent. W szczególności opisuje sposób użycia w projektach gotowych modułów funkcjonalnych przygotowanych przez prowadzącego.

Dokument omawia specyficzne zagadnienia związane z użyciem sygnałów zegarowych, opisuje poszczególne moduły oraz przedstawia projekty z przykładami ich zastosowań w środowisku Xilinx ISE. Zawarte w nim informacje są uzupełnieniem źródeł podstawowych nt. zestawów S3EStarter: „Spartan-3E Starter Kit Board User Guide” (ug230.pdf, http://www.xilinx.com/) oraz dokumentacji katalogowej układów umieszczonych na płycie.

Opisane moduły zostały

przygotowane na potrzeby projektów wykonywanych w ramach zajęć przedmiotu

„Układy cyfrowe i systemy wbudowane” i są udostępnione wyłącznie dla prywatnych

celów edukacyjnych.

SPIS TREŚCI

Częstotliwość

podstawowa 50 MHz

Akcelerometr

ADXL345 (płyta GY-273)

Magnetometr

HMC5883L (płyta GY-291)

OLED128x64

– tryb auto horizontal scroll

Oryginalne

pliki konfiguracyjne płyty

Sygnały zegarowe

Większość projektów powinna korzystać z jednego sygnału zegarowego o częstotliwości 50 MHz, jednak w niektórych przypadkach konieczne jest użycie zegara o innej częstotliwości, bądź przygotowanie projektu, którym występuje wiele różnych częstotliwości.

Częstotliwość

podstawowa 50 MHz

Sygnał 50 MHz dostępny jest na wyprowadzeniu C9 i powinien być traktowany jako podstawowe źródło synchronizacji układu. Plik GenIO.UCF zawiera kompletną definicję tego wyprowadzenia, która powinna być dołączana do każdego projektu.

Oprócz definicji położenia i standardu WE/WY (LOC i IOSTANDARD), w pliku tym podana jest też specyfikacja częstotliwości (PERIOD = 20.0ns), która jest podstawą analiz czasowych wykonywanych przy przez narzędzie PAR (Place And Route) podczas implementacji projektu. Po implementacji warto sprawdzić w raportach, czy projekt spełnił zależności czasowe wynikające z podanej szybkości zegara (View Design Summary > Timing Constraints) i czy nie zostały zgłoszone błędy Timing constraint not met.

Częstotliwości

niestandardowe

Niektóre moduły obsługujące specyficzne urządzenia WE/WY wymagają podania częstotliwości wzorcowej o wartości różnej od standardowych 50 MHZ, np. 60 MHz dla USB lub 75 MHz dla pamięci DDR RAM. W takim przypadku konieczne jest użycie elementu DCM_SP (Digital Clock Manager), który w układach Spartan3 umożliwia precyzyjną syntezę częstotliwości.

Syntezowana sygnał pobierany jest z wyprowadzenia CLKFX, a jego częstotliwość jest równa Fclkin * CLKFX_MULTIPLY / CLKFX_DIVIDE, gdzie mnożnik i dzielnik podaje się jako atrybuty elementu DCM. Ponadto, stosując ten element należy także poprowadzić sygnał sprzężenia zwrotnego CLKFB jak na rysunku. Szczegóły zawiera przykładowy projekt Test_LCDWrite (w którym jest syntezowany sygnał CLKFX o częstotliwości 90 MHz) i na nim należy się na razie wzorować. Element DCM_SP zostanie omówione na wykładzie, gdy przyjdzie jego kolej.

Projekty

wielodomenowe

Jeśli całość projektu z różnych przyczyn nie może pracować z jedną częstotliwością (np. jednoczesne użycie modułu VGA 50MHz oraz USB 60 MHz), w projekcie będą występowały rozłączne obszary taktowane z różną częstotliwością – tzw. domeny zegarowe. Problemem wówczas staje się analiza czasowa sygnałów przechodzących pomiędzy domenami, gdyż wymaga ona zdefiniowania specjalnych warunków. W naszych przypadkach należy ją po prostu wyłączyć, aby nie generowała fałszywych alarmów Timing constraint i – przede wszystkim – aby nie wypaczyła optymalizacji przeprowadzanych przez narzędzie PAR.

Projekt Test_LCDWrite zawiera przykład takiej sytuacji. Aby to zrobić, należy:

1) nadać połączeniom zegarowym na schemacie szczytowym nazwy znaczące, np. Clk50 oraz ClkSys,

2) w pliku UCF zdefiniować domeny poleceniem TNM (Timing Name) oraz dodać polecenia TIG (Timing Ignore):

# Ignore

cross-clock domain data paths in timing analysis

NET

"Clk50" TNM =

"TNM_Clk50";

NET "ClkSys" TNM = "TNM_ClkSys";

TIMESPEC

"TS_12" = FROM "TNM_ClkSys" TO

"TNM_Clk50" TIG;

TIMESPEC

"TS_13" = FROM "TNM_Clk50"

TO "TNM_ClkSys" TIG;

"TS_12", "TS_13" są identyfikatorami poleceń TIMESPEC i w dodawanych kolejnych powinny być unikalne. Plik GenIO.ucf zawiera szablony powyższych poleceń. Więcej szczegółów nt. analizy czasowej sygnałów w Software Manuals > Constraints Guide.

Pliki

UCF

W projektach należy korzystać z kompletnych specyfikacji UCF, które są podane w „Spartan-3E Starter Kit Board User Guide” i które oprócz przypisania sygnału do wyprowadzenia często podają szereg parametrów trybu pracy WE/WY (wydajności prądowe, rezystory pull-up / pull-down etc.). W poniższych plikach zebrano grupy sygnałów, które sterują urządzeniami wykorzystywanymi w projektach:

[GenIO.ucf (zip)] – Clk_50MHz, BTN_*,

SW(3:0), ROT_*, LED(7:0),

PS/2, VGA, RS-232

[LCD.ucf (zip)] – wyświetlacz LCD

[ADC_DAC.ucf

(zip)] – przetworniki ADC /

DAC

[PHY.ucf (zip)] – sterownik PHY (Ethernet)

[PS2_USB_SDC.ucf (zip)] – płyta zewnętrzna z gniazdami PS2, USB oraz SDCard

[DDR_SDRAM.ucf

(zip)] – pamięć DDR SDRAM

[1-Wire_J4.ucf (zip)] – układ 1-Wire dołączony do gniazda

J4

[Magneto_J4.ucf (zip)] – płyta GY-273 (magnetometr) dołączona

do gniazda J4

[Accel_J4.ucf (zip)] – płyta GY-291 (akcelerometr)

dołączona do gniazda J4

[OLED_J4.ucf (zip)] – wyświetlacz OLED128x64 dołączony

do gniazda J4

Moduły

Aby użyć dowolny moduł należy rozpakować wszystkie pliki z jego archiwum ZIP do głównego folderu projektu – od tego momentu będzie można umieszczać jego symbole na schematach. W środowisku ISE NIE należy dodawać żadnych plików z archiwum do projektu.

Większość modułów jest przygotowana do pracy w projektach z wieloma domenami zegarowymi i posiada dwa wejścia synchronizujące: wejście częstotliwości wzorcowej, wymaganej do pracy modułu (najczęściej Clk_50MHz), oraz wejście Clk_Sys dla zegara systemowego. W projektach z jedną domeną zegarową na oba wejścia należy podać ten sam sygnał.

Poniżej podano opisy poszczególnych modułów. Jeśli nie zaznaczono tego inaczej:

· wszystkie WE / WY są synchroniczne względem Clk_Sys i aktywne stanem wysokim (tzn. np. funkcja WE jest aktywowana gdy dane wejście ma wartość ‘1’ w momencie zbocza rosnącego zegara),

· w symbolach na lewej krawędzi umieszczone są sygnały wejściowe, na prawej wyjściowe.

RotaryEnc

Moduł ten dekoduje sygnały przełącznika obrotowego.

Każdy ruch przełącznika (tj. 1 skok) sygnalizowany jest jednotaktowym impulsem na wyjściu RotL (obrót w lewo) lub RotR (obrót w prawo). Impulsy są synchroniczne względem sygnału Clk, zatem moduł RotaryEnc powinien być synchronizowany tym samym sygnałem, co moduł odczytujący impulsy Rot*.

Wejścia ROT_A oraz ROT_B należy dołączyć wprost do wyprowadzeń zewnętrznych.

Plik UCF: GenIO.ucf.

Przykłady użycia: Test_LCD1x64, Test_LCD2x64, Test_KbdVGA.

PS2_Rx

Moduł ten jest odbiornikiem bajtów odczytywanych z portu PS/2.

Sygnał DO_Rdy = ‘1’ sygnalizuje zakończenie odbioru bajtu (impuls jednotaktowy); na DO(7:0) podawana jest wówczas jego wartość. Sygnał DO pozostaje stabilny do czasu następnej transmisji PS/2, w praktyce przez co najmniej kilkadziesiąt milisekund.

Sygnały PS2_Clk oraz PS2_Data należy dołączyć wprost do wyprowadzeń zewnętrznych.

Plik UCF: GenIO.ucf.

Przykłady użycia: Test_PS2Rx_RS.

PS2_Kbd

Moduł ten jest odbiornikiem kodów wysyłanych przez klawiaturę PS/2.

Sygnał DO_Rdy = ‘1’ sygnalizuje zakończenie odbioru kodu (impuls jednotaktowy); na DO(7:0) podawana jest wówczas jego wartość, a wyjścia E0 oraz F0 sygnalizują, czy był on poprzedzony bajtami X”E0” (tzw. kod rozszerzony) oraz X”F0” (kod zwolnienia klawisza). Odbiór samych bajtów X”E0” oraz X”F0” nie jest sygnalizowany. Sygnały DO, E0 oraz F0 pozostają stabilne do czasu następnej transmisji klawiatury, w praktyce przez co najmniej kilkadziesiąt milisekund.

Sygnały PS2_Clk oraz PS2_Data należy dołączyć wprost do wyprowadzeń zewnętrznych.

Plik UCF: GenIO.ucf.

Przykłady użycia: Test_KbdLCD, Test_KbdVGA.

W projekcie Test_KbdLCD moduł KbdDecode pokazuje przykład prostego dekodowania wybranych klawiszy i ich zamiany na sygnały sterujące – w tym przypadku wyświetlaczem LCD.

PS2_Mouse

Moduł ten jest odbiornikiem kodów wysyłanych przez mysz PS/2. Każde zdarzenie (naciśnięcie / zwolnienie przycisku myszy lub jej poruszenie) spowoduje odbiór 3 bajtów: statusu, przesunięcia w poziomie oraz przesunięcia w pionie.

Sygnał DataRdy= ‘1’ sygnalizuje odbiór bajtów (impuls jednotaktowy), natomiast ich wartości są wyprowadzane na wyjścia B1_Status, B2_X oraz B3_Y i nie zmieniają się do początku odbioru kolejnej transmisji.

Po zerowaniu modułu automatycznie wykonywana jest inicjalizacja myszy; należy odczekać, aż INIT_OK = ‘1’.

Sygnały PS2_Clk oraz PS2_Data należy dołączyć wprost do wyprowadzeń zewnętrznych.

Plik UCF: GenIO.ucf.

Przykład użycia: Test_PS2Mouse.

RS232_Tx

Moduł ten obsługuje nadawanie bajtów do portu RS-232.

Jednotaktowy impuls TxStart rozpoczyna operację nadawania bajtu TxDI i ustawia sygnał TxBusy = ‘1’. Tak długo, jak trwa TxBusy = ‘1’, impulsy TxStart są ignorowane. Bajt TxDI jest zatrzaskiwany gdy TxStart= ‘1’ i nie musi pozostać stabilny podczas trwania transmisji.

Sygnał RS232_TxD należy dołączyć wprost do wyprowadzenia zewnętrznego.

Plik UCF: GenIO.ucf.

RS232

Moduł obsługuje dwukierunkową komunikację RS-232 full-duplex. Parametry transmisji podane są obok symbolu.

Jednotaktowy impuls TxStart rozpoczyna operację nadawania bajtu TxDI i ustawia sygnał TxBusy = ‘1’. Tak długo, jak trwa TxBusy = ‘1’, impulsy TxStart są ignorowane. Bajt TxDI jest zatrzaskiwany gdy TxStart= ‘1’ i nie musi pozostać stabilny podczas trwania transmisji.

Pojawienie się jednotaktowego impulsu na RxRdy sygnalizuje zakończenie odbioru bajtu, który jest gotowy do odczytu na wyjściu RxDO. Jego wartość pozostaje niezmienna do początku kolejnej transmisji Rx.

Możliwa jest pełna praca dupleks, tzn. jednoczesny odbiór i nadawanie.

Sygnały RS232_RxD oraz RS232_TxD należy dołączyć wprost do wyprowadzeń zewnętrznych.

Plik UCF: GenIO.ucf.

Przykład użycia: Test_RS2LCD, Test_RS232.

LCD1x64,

LCD2x64

Moduły te są najprostszymi w użyciu wyświetlaczami wartości heksadecymalnych na LCD. Moduł LCD1x64 używa jednej, natomiast LCD2x64 obu linii wyświetlacza. Wyświetlane są 64–bitowe liczby z wejść Line* (16 znaków w linii * 4b na znak), natomiast wejścia Blank* określają dodatkowo, które znaki mają być wygaszone ( Blank*( i ) = ‘1’ <=> cyfra nr i nie jest wyświetlana).

Wejścia Line* oraz Blank* mogą zmieniać się asynchronicznie względem Clk_50MHz (bezwładność LCD i tak nie pozwoli zauważyć pojawiających się ewentualnych przekłamań), dzięki czemu w tym przypadku wyjątkowo nie jest wymagany osobny sygnał Clk_Sys. Jeśli jednak występuje on w projekcie, ma częstotliwość różną od 50 MHz i synchronizuje sygnały podawane na wejścia Line / Blank, aby wyeliminować fałszywe komunikaty błędów należy wyłączyć analizę czasową sygnałów przechodzących z domeny Clk_Sys do Clk_50MHz, jak zostało to opisane powyżej.

Sygnały LCD_* oraz SF_CE należy dołączyć wprost do wyprowadzeń zewnętrznych.

Plik UCF: LCD.ucf.

Przykłady użycia: Test_LCD1x64, Test_LCD2x64.

LCDWrite

Moduł ten obsługuje komunikację ze sterownikiem wyświetlacza LCD f-my Sitronix (odpowiednik HD44780) i umożliwia jego (prawie) pełną kontrolę. Automatycznie wykonuje odpowiednie procedury inicjalizacyjne, konwersję szerokości magistral 4 / 8b oraz testowanie flagi zajętości. Możliwy jest tylko zapis bajtu (brak odczytu – stąd „prawie pełna” kontrola).

Po inicjalizacji automatycznie ustawiane są odpowiednie parametry pracy sterownika; sygnały z wejść Blink oraz Cursor są wówczas próbkowane i decydują o sposobie wyświetlania kursora. Gdy Busy zmieni się na 0, moduł gotowy jest do pracy.

Operację zapisu inicjalizuje jednotaktowy impuls WE (Write Enable). Bajt danych DI(7:0) oraz bit sterujący DnI (Data not Instruction, nazywany w HD44780 Register Select, RS) powinny być ustawione zgodnie z oczekiwana funkcją. Sygnał Busy = ‘1’ oznacza brak gotowości i wówczas impulsy WE są ignorowane. Dane DI oraz DnI są zatrzaskiwane i nie muszą pozostać stabilne, gdy Busy = ‘1’.

Opis sterowania pracą wyświetlacza, kody sterujące, jakie należy podać na wejścia DI oraz DnI itp. są dostępne w dokumencie f-my Sitronix.

Sygnały LCD_* oraz SF_CE należy dołączyć wprost do wyprowadzeń zewnętrznych.

Plik UCF: LCD.ucf.

Przykład użycia: Test_LCDWrite.

VGAtxt48x20

Moduł ten jest prostym terminalem znakowym wyświetlającym 20 linie po 48 znaków każda. Możliwe są podstawowe operacje przenoszenia kursora oraz automatyczne przewijanie ekranu.

Początkowo pozycją bieżącą jest (0, 0). Jednotaktowy impuls Char_WE powoduje zapis na niej znaku o kodzie ASCII z Char_DI oraz jej automatyczną inkrementację. Po dojściu do ostatniej kolumny pozycja bieżąca automatycznie przechodzi do następnej linii, ponadto można ją zmieniać jednotaktowymi impulsami sygnałów Home, NewLine oraz Goto00. Gdy CursorOn = ‘1’, na bieżącej pozycji wyświetlany jest kursor.

Wyświetlany jest zestaw 128 znaków ASCII, bit Char_DI(7) jest ignorowany. Kształty znaków o kodach X"00" - X"1F" podane są tutaj.

Przewijanie ekranu jest wykonywane, gdy bieżąca pozycja opuszcza ostatnia linię i ScrollEn = ‘1’. Gdy ScrollEn = ‘0’, pozycją następną po ostatniej linii jest (0, 0).

Ponadto gdy ScrollEn = ScrollClear = ‘1’, przewinięcie ekranu powoduje automatyczne wyczyszczenie nowej linii, które trwa 48 taktów i na ten przedział ustawia flagę Busy = ‘1’. W tym czasie ignorowane są wszystkie polecenia. Gdy ScrollEn = ‘1’ i ScrollClear = ‘0’, w nowej linii pokaże się stara zawartość; bufor cykliczny ma pojemność 32 linii.

Za wyjątkiem czyszczenia nowej linii (ScrollEn = ScrollClear = ‘1’), wszystkie operacje wykonywane są w 1 takcie i flaga Busy nie jest ustawiana.

Schemat powyżej pokazuje przykład dołączenia modułu do wyprowadzeń zewnętrznych, które sterują portem VGA.

Plik UCF: GenIO.ucf.

Przykład użycia: Test_KbdVGA, Test_VGAscan (zawiera uniwersalną jednostkę skanującą port VGA do plików BMP podczas symulacji) , Test_SDCard, Test_USB.

DACWrite

Moduł obsługuje wysyłanie danych do przetwornika cyfra/analog LTC2624. Impuls Start = ‘1’ zatrzaskuje dane na wejściach Cmd, Addr i DATA oraz rozpoczyna ich szeregowe wysłanie do układu. Czas trwania operacji sygnalizuje wyjście Busy.

10 wyjść modułu przeznaczonych jest do dołączenia do wyprowadzeń zewnętrznych FPGA. Oprócz sygnałów używanych do właściwej komunikacji z przetwornikiem zawierają one szereg innych sygnałów trwale blokujących pozostałe urządzenia na płycie korzystające z magistrali SPI: przetwornik ADC, jego przedwzmacniacz oraz trzy rodzaje pamięci flash. Jeśli elementy te mają być używane w projekcie, należy samodzielnie zrealizować odpowiedni arbitraż.

Plik UCF: ADC_DAC.ucf.

Przykład użycia: Test_WAVreader.

ADC_Ctrl

Moduł steruje przetwornikiem analog/cyfra LTC1407 oraz jego przedwzmacniaczem LTC6912. Przy komunikacji ze wzmacniaczem po podaniu impulsu AMP_WE = ‘1’ słowo do wysłania jest pobierane z wejścia AMP_DI. Impuls ADC_Start = ‘1’ powoduje wysłanie sygnału CONV do przetwornika oraz odczyt poprzednich pomiarów jego obu kanałów, które następnie są widoczne na wyjściach ADC_DOA oraz ADC_DOB. Koniec obu operacji sygnalizuje Busy = ‘0’.

Podobnie jak w przypadku modułu DACWrite 12 wyjść przeznaczonych do połączenia z wyprowadzeniami zewnętrznymi steruje pracą także innych urządzeń wykorzystujących magistralę SPI na płycie – patrz uwaga powyżej nt. ich ewentualnego arbitrażu.

Plik UCF: ADC_DAC.ucf.

PHY_Rx

Moduł odbiornika transmisji Ethernet przeznaczony do pracy w

domenie zegarowej 75 MHz. Nadchodzące bajty umieszczane są w 2kB kolejce FIFO

wraz z atrybutem oznaczającym koniec ramki bądź wystąpienie błędu:

AtrO =

‘0’ – na wyjściu DO poprawnie

odebrany bajt danych

AtrO =

‘1’, DO

= X”

AtrO =

‘1’, DO

= X”FF” – błąd transmisji.

Sygnał FIFO_POP służy do usunięcia bajtu z kolejki, wyjścia Empty oraz Full sygnalizują jej stan.

Plik UCF: PHY.ucf.

PHY_Tx

Moduł nadajnika transmisji Ethernet przeznaczony do pracy w domenie zegarowej 75 MHz. Bajty skierowane do wysłania wpisywane są do 2kB kolejki FIFO wraz z atrybutem AtrI = ‘0’; wpisanie dowolnego bajtu z AtrI = ‘1’ jest sygnałem końca ramki (deaktywowany jest wówczas sygnał E_Tx_En na czas odpowiadający transmisji 128B). Do obsługi kolejki przeznaczone są sygnały PUSH, FIFO_Full oraz FIFO_Empty.

Transmisja ramki rozpoczyna się natychmiast po wpisaniu pierwszego bajtu do pustej kolejki, natomiast zostanie zakończona także w przypadku jej opróżnienia, zatem należy zadbać o odpowiednie tempo wpisu (co najmniej 12.5 MB/s dla łącza 100 Mbps i 1.25 MB/s dla łącza 10 Mbps).

Plik UCF: PHY.ucf.

SDC_FileReader

Moduł ten odczytuje plik o zadanej nazwie z karty pamięci flash typu Secure Digital. Wymaga dołączenia zewnętrznej płyty rozszerzającej z gniazdem SDCard. Wyjściowy strumień bajtów jest buforowany w kolejce FIFO i może być odczytywany w dowolnym tempie (odczyt kolejnych sektorów pliku jest automatycznie wstrzymywany do czasu dostatecznego opróżnienia kolejki). Używany jest interfejs SPI karty i maksymalna szybkość odczytu wynosi ok. 3 MB/s.

Aby odczyt pliku był możliwy muszą być spełnione następujące

warunki:

– karta w formacie FAT16 lub FAT32 z rozmiarem jednostki alokacji od 8 do 64kB,

– nazwa pliku składa się z jednego znaku + rozszerzenie „bin”, „txt”, „wav” lub

puste,

– plik znajduje się w katalogu głównym.

Jednotaktowy impuls Start

rozpoczyna odczyt i powoduje ustawienie Busy = ‘1’. Nazwę pliku należy podać na port FName (1

znak ASCII), natomiast rozszerzenie na port FExt wg zasady:

FExt(1:0) = "00" => " "

FExt(1:0) =

"01" => "BIN"

FExt(1:0) =

"10" => "TXT"

FExt(1:0) =

"11" => "WAV"

Sygnał Abort przerywa

odczyt; zakończenie pracy i stan gotowości (Busy = ‘0’) może nie być

natychmiastowe.

Odczyt strumienia bajtów sprowadza się do obsługi kolejki FIFO. Sygnał DO_Rdy = ‘1’ oznacza, że na wyjściu DO znajduje się gotowy bajt do odczytu. Przejście do następnego bajtu następuje przez podanie impulsu DO_Pop = ‘1’.

Koniec odczytu następuje, gdy Busy = DO_Rdy = ‘0’.

Jeśli podczas pracy modułu wystąpi błąd, na dwubitowym

wyjściu Error pojawi się jego

kod:

00

=> błąd inicjalizacji karty

01 => zły format karty

10 => nie odnaleziono pliku

11 => praca poprawna (bez błędu)

Kod błędu jest kasowany impulsami Reset

oraz Start.

Sygnały SDC_* należy dołączyć wprost do wyprowadzeń zewnętrznych.

Plik UCF: PS2_USB_SDC.ucf.

Przykład użycia: Test_SDCard.

WAVreader

Moduł ten odczytuje plik dźwiękowy WAV o zadanej nazwie z karty pamięci flash typu Secure Digital (zewnętrzna płyta rozszerzająca z gniazdem SDCard) i udostępnia jego zawartość jako strumień próbek na wyjściach DO_L / DO_R.

Do odczytu pliku używany jest moduł SDC_FileReader

i muszą być spełnione jego warunki dotyczące formatu karty. Plik dźwiękowy musi

znajdować się w katalogu głównym karty i spełniać następujące warunki:

- nazwa składająca się z jednego znaku, podanego w kodzie ASCII na wejściu FName;

- rozszerzenie „WAV”;

- format mono lub stereo;

- rozmiar próbek 8 lub 16b;

- max. częstotliwość próbkowania 65535Hz.

Moduł automatycznie rozszerza próbki 8b do 16b, a w przypadku plików mono

powiela ten sam strumień na obu wyjściach DO_*.

Wartości próbek podawane są w naturalnym kodzie binarnym.

Jednotaktowy impuls Start rozpoczyna odczyt (nazwa pliku musi być podana na wejściu FName) i powoduje ustawienie Busy = ‘1’. Sygnał DO_Rdy = ‘1’ oznacza, że na wyjściach DO_* znajdują się próbki gotowe do odczytu. Przejście do następnych próbek następuje przez podanie impulsu DO_Pop = ‘1’. Koniec odczytu następuje, gdy Busy = DO_Rdy = ‘0’. Sygnał Abort przerywa odczyt; zakończenie pracy i przejście w stan gotowości (Busy = ‘0’) może nie być natychmiastowe. Podobnie jak w przypadku modułu SDC_FileReader, strumień próbek jest buforowany w kolejce FIFO i może być odczytywany w dowolnym tempie.

Moduł

udostępnia informacje o odtwarzanym pliku na odpowiednich wyjściach:

FmtMnS (Format

Mono / not Stereo): 1 = Mono / 0 = Stereo

Fmt8n16

(Format 8 / not 16b): 1 = próbki 8b /

0 = próbki 16b

FmtSRate (Format

Sample Rate): ilość

próbek na sekundę (liczba 16b)

Dodatkowo, na wyjściu SRate_Tick generowane są jednotaktowe impulsy synchroniczne względem sygnału Clk_Sys o częstotliwości odpowiadającej parametrowi FmtSRate, które można wykorzystać przy wysyłaniu próbek do przetwornika DAC.

Jeśli podczas pracy modułu pojawi się błąd, na wyjściu Error pojawi się jego kod i praca

zostanie przerwana:

Error

= "000" => błąd inicjalizacji karty

Error = "001" => zły

format karty

Error = "010" => nie

odnaleziono pliku o podanej nazwie

Error = "100" => błąd

formatu WAV

Error = "101" => złe

parametry formatu WAV

Error = "111" => praca

poprawna (brak błędu)

Kod błędu jest kasowany impulsami Reset

oraz Start.

Sygnały SDC_* należy dołączyć wprost do wyprowadzeń zewnętrznych.

Plik UCF: PS2_USB_SDC.ucf.

Przykład użycia: Test_WAVreader.

USB_Function

Moduł ten jest kompletnym urządzeniem USB udostępniającym dwa punkty końcowe: endpoint 0 – transfery kontrolne (dwukierunkowe) oraz endpoint 1 – transfery masowe out (od hosta do urządzenia). Obsługuje ponadto procedurę enumeracji, która umożliwia automatyczne wykrycie urządzenia przez hosta USB po podłączeniu. Urządzenie pracuje z szybkością full speed, tzn. 12 Mbps.

Transfery kontrolne przeznaczone są do dwukierunkowego przesyłania niewielkich ilości danych. Moduł wykorzystuje w tym celu transakcje Vendor-specific Control Read. Przesyłane są dwa bajty: odebrane od hosta pojawiają się na wyjściu VCR_DO, wysyłane do hosta pobierane są z wejścia VCR_DI. Zakończenie całego dwukierunkowego transferu sygnalizowane jest impulsem VCR_Done. Standard USB nie daje możliwości zasygnalizowania, że nastąpi transfer kontrolny i należy przygotować dane na porcie VCR_DI; urządzenie informuje tylko po fakcie, że zostały one wysłane i że należy przygotować następne. Analogicznie, nie ma specjalnego sygnału synchronizującego zmiany sygnału VCR_DI i dlatego powinien on pozostawać stabilny przez cały czas, gdy oczekujemy na transakcję VCR.

Transfer masowy przeznaczony jest do przekazywania dużych ilości danych i w tym module możliwy jest wyłącznie w kierunku od hosta do urządzenia (Out Bulk Transfer). Niewielka kolejka FIFO o pojemności 16B zapewnia proste buforowanie nadchodzących danych, lecz przy braku odbioru przepełnia się już po ok. 10 us, sygnalizując to na wyjściu Bulk_OVL. Obsługa odbioru sprowadza się do odczytu strumienia danych z kolejki FIFO: Bulk_Rdy = ‘1’ oznacza obecność kolejnego bajtu na magistrali Bulk_DO, impulsem Bulk_POP = ‘1’ następuje przejście do następnego.

Szczegóły obsługi urządzenia od strony hosta można poznać na przykładzie aplikacji C++ zawartej w projekcie Test_USB.

Sygnały USB_D* należy dołączyć wprost do wyprowadzeń zewnętrznych.

Plik UCF: PS2_USB_SDC.ucf.

Przykład użycia: Test_USB.

DDR

Moduł ten jest uproszczonym sterownikiem pamięci DDR SDRAM, która znajduje się na płycie. Umożliwia wykonywanie wszystkich komend DRAM, lecz ogranicza szybkość wykonywanych operacji nie zezwalając na ich nakładanie się (niemożliwe są więc np. odczyty Read Afer Read itp.). Zawiera dodatkowo układ czasowy, który można wykorzystać do organizacji cykli odświeżania.

Użycie modułu wymaga zrozumienia zasad pracy pamięci DDR SDRAM – pomocny może tu być opis zawarty w standardzie Double Data Rate (DDR) SDRAM Specification (JESD79E.pdf, www.jedec.org) oraz dane katalogowe 512Mb DDR SDRAM (x4, x8, x16) Component Data Sheet (512MBDDRx4x8x16.pdf, www.micron.com). Przykład Test_DDR, w szczególności sposób pracy zawartej w nim maszyny stanów FSM_TestDDR, powinien pomóc w zrozumieniu zasad posługiwania się tym modułem.

Synchronizacja

Moduł przeznaczony jest do pracy z częstotliwością Clk_In równą 75 MHz. Przy implementacji wymagane jest podanie specyficznych poleceń TIG oraz FEEDBACK, których szablony znajdują się w pliku UCF (należy w nich tylko uzupełnić nazwę instancji modułu na schemacie głównym). Należy sprawdzać w raportach analizy czasowej, czy implementacja dla zadanej częstotliwości powiodła się.

Ze względu na specyficzne problemy synchronizacji transferu DDR, wewnątrz modułu użyte są dwa elementy DCM, które generują szereg pochodnych sygnałów synchronizujących, w tym sygnał dla synchronizacji pracy całego systemu – Clk_Out. Ma on tę samą częstotliwość, co Clk_In i to on ( a nie Clk_In) powinien być użyty w projekcie jako zegar systemowy ClkSys. Aby uniknąć problemów podczas implementacji, należy dokładnie powielić rozwiązanie, jakie jest zastosowane w przykładzie Test_DDR. Wszystkie sygnały WE / WY modułu powinny być / są synchroniczne względem Clk_Out.

Organizacja pamięci

Układ MT46V32M16 o łącznej pojemności 512 Mb ma organizację 32M x 16 x 4 banki. Każdym banku znajduje się 8k wierszy, każdy po 1k słów 16b. Moduł DDR konfiguruje pamięć do pracy z parametrami Burst Length = 2 oraz CAS Latency = 2. Każda operacja zapisu / odczytu przekazuje dwa słowa 16b, które są podawane równolegle na magistralach WrD oraz RxQ (stąd ich rozmiar 32b). Dzięki temu potokowa natura transferu DDR jest niewidoczna i przy obsłudze modułu można dla uproszczenia przyjąć, że każdy wiersz pamięci ma organizację 512 słów 32b – przy dostępie do nich należy tylko pamiętać, aby najmłodszy bit adresowy A( 0 ) był równy zero.

Komendy

Podczas inicjalizacji moduł automatycznie konfiguruje pamięć oraz przeprowadza kalibrację opóźnień czasowych wymaganych przy odczycie (zaimplementowane rozwiązanie nie używa sygnałów DQS i zamiast nich korzysta ze zmiennej korekcji fazy, jaka jest możliwa w elementach DCM układów Spartan-3). Gdy Busy = ‘0’, moduł jest gotowy do pracy.

Poniższy pakiet z pliku DDR_Commands.vhd (do dołączenia w projekcie) zawiera definicje komend rozpoznawanych przez moduł:

package DDR_Commands is

constant CMD_NOP : std_logic_vector(

2 downto 0 ) := "000";

constant CMD_Active : std_logic_vector(

2 downto 0 ) := "001";

constant CMD_Read : std_logic_vector(

2 downto 0 ) := "010";

constant CMD_Write : std_logic_vector(

2 downto 0 ) := "011";

constant CMD_Precharge:

std_logic_vector( 2 downto

0 ) := "100";

constant CMD_PreAll : std_logic_vector(

2 downto 0 ) := "101";

constant CMD_AutoRefr

: std_logic_vector( 2 downto

0 ) := "110";

end DDR_Commands;

Podanie na wejściu Cmd jakiejkolwiek wartości różnej od Cmd_NOP rozpoczyna operację oraz ustawia flagę BUSY = ‘1’. Do czasu jej skasowania żadne inne polecenia nie są akceptowane. Przyjęcie komendy powoduje zatrzaśnięcie wartości znajdujących się na wejściach BA oraz A. Dla CMD_Write dane są zatrzaskiwane także na wejściu WrD. Po zakończeniu operacji CMD_Read dane na wyjściu RdQ pozostają niezmienne aż do następnego odczytu.

Typowo, praca z modułem DDR polega na otwarciu wybranego wiersza (Cmd_Active), wykonaniu operacji zapisu / odczytu (Cmd_Write / Cmd_Read) oraz zamknięciu wiersza (Cmd_Precharge / Cmd_PreAll). Z odpowiednią częstotliwością należy także wykonywać operacje odświeżania (Cmd_AutoRefr), pamiętając o uprzednim zamknięciu wierszy we wszystkich bankach (Cmd_PreAll).

Sygnał RefReq jest ustawiany po ok. 7,5 ms od ostatniego odświeżania – ponieważ wymagany interwał wynosi 7,8 ms, daje to ok. 0,3 ms (22 takty) czasu na reakcję.

Plik UCF: DDR_SDRAM.ucf.

Przykład użycia: Test_DDR.

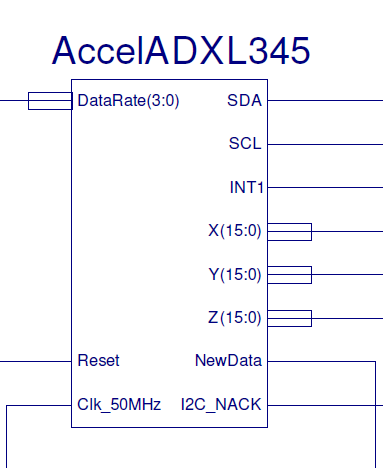

Akcelerometr ADXL345 (płyta GY-273)

Moduł jest kompletnym sterownikiem akcelerometru ADXL345: wykonuje jednokrotnie jego inicjalizację (ciągły tryb pomiarowy z częstotliwością wynikającą z podanej wartości DataRate, domyślny zakres +/- 2g), a następnie w pętli odczytuje wyniki udostępniając je na portach X, Y oraz Z. Każdy nowy odczyt jest sygnalizowany jednotaktowym impulsem NewData.

Porty WE:

DataRate

– bity D(3:0) rejestru BW_RATE (adres 0x2C) wysyłane

jednorazowo podczas inicjalizacji, a określające częstotliwość pomiarów.

Porty WY:

X, Y, Z –

odczytane wartości przyspieszeń.

NewData

– sygnalizacja pojawienia się nowego pomiaru (impuls jednotaktowy).

I2C_NACK – wyjście ustawiane przez

moduł komunikacji I2C w przypadku błędu zapisu do urządzenia (Negative Akcnowledge),

kasowane sygnałem Reset.

Wyprowadzenia

zewnętrzne:

SDA, SCL, INT1

– połączenia z płytą GY-273 (do przypisania w pliku UCF).

Plik UCF: Accel_J4.ucf.

Przykład użycia: Test_Accel.

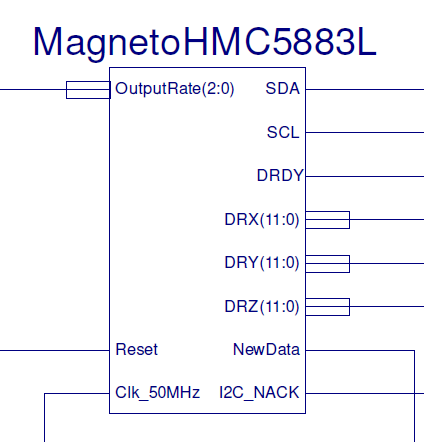

Magnetometr HMC5883L (płyta GY-291)

Moduł jest kompletnym sterownikiem magnetometru HMC5883L: wykonuje jednokrotnie jego inicjalizację (ciągły tryb pomiarów z częstotliwością wynikającą z podanej wartości OutputRate, zakres +/- 0.88Ga, uśrednianie 8 próbek) , a następnie w pętli odczytuje wyniki udostępniając je na portach DRX, DRY oraz DRZ. Każdy nowy odczyt jest sygnalizowany jednotaktowym impulsem NewData.

Porty WE:

OutputRate

– bity (4:2) rejestru

konfiguracyjnego A (adres 0x00) wysyłane jednorazowo podczas inicjalizacji, a

określające częstotliwość pomiarów.

Porty WY:

DRX, DRY, DRZ –

odczytane natężenia pola magnetycznego.

NewData

– sygnalizacja pojawienia się nowego pomiaru (impuls jednotaktowy).

I2C_NACK – wyjście ustawiane

przez moduł komunikacji I2C w przypadku błędu zapisu do urządzenia (Negative Akcnowledge),

kasowane sygnałem Reset.

Wyprowadzenia

zewnętrzne:

SDA, SCL, DRDY

– połączenia z płytą GY-291 (do przypisania w pliku UCF).

Plik UCF: Magneto_J4.ucf.

Przykład użycia: Test_Magneto.

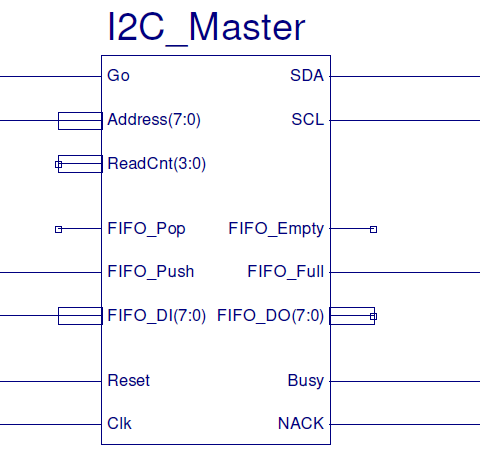

I2C_Master

Uniwersalny moduł sterownika magistrali I2C w trybie Fast-mode (400kbps) z 16B kolejką FIFO na buforowanie przekazywanych danych. W transmisjach wejściowych umożliwia odczyt maksymalnie 16 bajtów, transmisje wyjściowe trwają do opróżnienia kolejki (możliwe jest wysłanie dowolnej liczby bajtów, jeśli kolejka będzie uzupełniania w trakcie transmisji).

Porty WE:

Go – impuls rozpoczynający

transmisję; ignorowany, jeśli nie zakończyła się poprzednia i Busy = ‘1’.

Address

– pierwszy bajt transmisji zawierający adres urządzenia (bity 7:1) oraz

określenie jej kierunku (bit 0 = ‘0’ – output / ‘1’ – input).

ReadCnt

– ilość bajtów do odczytu w transmisjach typu input; zatrzaskiwana w momencie

startu transmisji wejściowej (Go

= ‘1’ oraz Address(0) = ‘1’), ignorowana w transmisjach

wyjściowych.

FIFO_Pop,

FIFO_Push

– komendy kolejki FIFO.

FIFO_DI – wpis na początek

kolejki FIFO.

PortyWY:

FIFO_Empty, FIFO_Full – status kolejki

FIFO.

FIFO_DO – bajt widoczny

na końcu kolejki FIFO.

Busy –

sygnał zajętości modułu (trwa transmisja).

NACK – sygnał braku

potwierdzenia odbioru bajtu przez urządzenie (błąd

logiczny transmisji, brak urządzenia, itp.); zerowany sygnałem Reset.

Wyprowadzenia

zewnętrzne:

SDA, SCL – wyprowadzenia magistrali I2C (do przypisania w

pliku UCF konkretnego urządzenia).

=> Podczas

transmisji WY dostępne jest cały czas wejście kolejki FIFO, tzn. sygnały FIFO_PUSH oraz FIFO_DI, natomiast ignorowany jest sygnał FIFO_Pop; można więc np. wypełnić kolejkę w czasie

nadawania bajtu adresu (po podaniu impulsu Go).

=> Podczas

transmisji WE dostępne jest cały czas wyjście kolejki FIFO, tzn. sygnały FIFO_POP oraz FIFO_DO, natomiast ignorowany jest sygnał FIFO_Push; z odczytem odbieranych bajtów nie trzeba

więc czekać na zakończenie całej transmisji.

=> Kolejka FIFO nie

jest automatycznie opróżniana na początku transmisji WE. Błędy jej

przepełnienia (zapis gdy FIFO_Full = ‘1’ lub odczyt gdy FIFO_Empty = ‘1’) nie są wykrywane i mogą spowodować

jej rozsynchronizowanie.

=> Czas transmisji

jednego bajtu wynosi 9 / 400×103 =

22.5ms, tj. 1125 taktów zegara 50MHz.

=> Moduł nie

obsługuje przełączania kierunku transmisji w jej trakcie (tzw. „start-without-stop condition”

dopuszczalne w protokole I2C); z rozpoczęciem kolejnej transmisji należy zawsze

odczekać aż Busy = ‘0’.

Plik UCF: zależny od urządzenia dołączonego do magistrali.

Przykład użycia: Test_OLED128x64 (z przykładem maszyny FSM obsługującej nadawanie), Test_I2C_Master (niesyntezowalny przykład do analizy pracy modułu w symulacji behawioralnej).

Ilustracje

zastosowań modułów

Poniżej zebrano przykładowe projekty, które pokazują sposób wykorzystania omówionych wyżej modułów. W archiwach ZIP znajdują się pliki źródłowe (*.sch, *.vhd, *.ucf, …), które po utworzeniu nowego projektu w środowisku ISE należy dodać do niego poleceniem Project > Add File…. Pominięto natomiast pliki z modułami, które są w projektach wykorzystywane – te należy skopiować z ich własnych archiwów ZIP.

W każdym archiwum znajduje się także plik BIT gotowy do zaprogramowania płyty i szybkiego testu jej pracy.

Test_I2C_Master

Plik symulacyjny (testbench) ilustrujący pracę modułu I2C_Master; kod niesyntezowalny, tylko do analizy zasad obsługi kolejek FIFO. Dodatkowo także przykład użycia procesu [Tbw_I2Cslave].

Test_LCD1x64

Dwa liczniki, zliczające impulsy przełącznika obrotowego, wyświetlane za pomocą modułu LCD1x64. Dodatkowo przełączniki SW(3:0) sterują wygaszaniem 4 środkowych cyfr wyświetlacza.

Test_LCD2x64

Jak w projekcie powyżej + 16b licznik w kodzie Johnsona sterowany przełącznikiem obrotowym, a użyty do wygaszania cyfr w dolnej linii wyświetlacza LCD.

Test_LCDWrite

Wyświetlenie napisu „Hello world!” na wyświetlaczu LCD.

Moduł FSM_String zawiera prostą maszynę stanów, która wysyła na LCD bajty odczytywane z pamięci ROM.

Wyłącznie tytułem przykładu, w tym projekcie zastosowano inną częstotliwość Clk_Sys (90 MHz) niż wymagane przez moduł LCD 50 MHz, tworząc projekt z dwiema domenami zegarowymi. Nie ma to wpływu na funkcjonalność układu.

Test_PS2Rx_RS

Wysyłanie bajtów odbieranych z portu PS/2 przez łącze RS-232.

Test_KbdLCD

Wyświetlanie znaków ‘0’ oraz ‘1’ odebranych z klawiatury na wyświetlaczu LCD + ustawianie kursora na początku pierwszej oraz drugiej linii wyświetlacza klawiszami Home oraz Enter.

Moduł KbdDecode jest prostym kombinacyjnym transkoderem bajtów otrzymywanych z klawiatury PS/2 (tu dla zwięzłości przykładu dekodowane są tylko klawisze ‘0’, ‘1’, Enter oraz Home).

Test_KbdVGA

Wyświetlanie na ekranie VGA kodów znaków odbieranych z klawiatury PS/2. Klawisze rozszerzone (E0) są pomijane, nie wyświetlane są także kody zwolnienia klawisza (F0). Przełącznik obrotowy steruje położeniem kursora generując polecenia Home i NewLine.

Moduł FSM_SendByte zawiera prostą maszynę stanów, która zamienia otrzymany bajt na dwa znaki ASCII. Ponadto moduł TBW_FSM_SendByte jest przykładem jej testu i pokazuje, jak można symulować procesami VHDL generowanie bajtów przez klawiaturę PS/2 oraz ustawianie flagi Busy prze moduł VGA.

Test_PS2Mouse

Wyświetlanie na LCD 3 bajtów wysyłanych przez mysz PS/2; dodatkowy licznik pokazuje ilość odebranych transmisji.

Test_RS2LCD

Test transmisji RS-232: wyświetlanie odebranych bajtów (Rx) na LCD oraz wysyłanie echa do Tx; dodatkowo licznik bajtów na LED.

Projekt wymaga połączenia płyty Spartan z portem szeregowym oraz uruchomienia programu obsługującego (np. hypertrm.exe, JRS_Term.exe), który ma ustawione odpowiednie parametry transmisji.

Test_RS232

(VGA)

Test transmisji RS-232: wysyłanie bajtów odbieranych z klawiatury PS/2 oraz wyświetlanie na ekranie VGA odbieranych znaków ASCII.

Projekt wymaga połączenia płyty Spartan z portem szeregowym oraz uruchomienia programu obsługującego (np. hypertrm.exe, JRS_Term.exe), który ma ustawione odpowiednie parametry transmisji.

Test_SDCard

Wyświetlanie na ekranie VGA zawartości pliku odczytanego z karty SecureDigital. Plik musi znajdować się w katalogu głównym karty i musi mieć nazwę „#.WAV”, gdzie # = 0 … 9 w zależności od ustawienia SW(3:0). Pozostałe wymogi odnośnie formatu karty w opisie modułu SDC_FileReader.

Sterowanie przełącznikiem obrotowym: RotL = start odczytu, RotR = kursor NewLine.

Test_WAVreader

Odtwarzanie w kanałach C i D przetwornika DAC pliku WAV odczytywanego z karty SecureDigital. Prosta maszyna stanów FSM_SendSamples zajmuje się pobieraniem próbek z modułu WAVreader oraz przekazywaniem ich do modułu DACWrite. Do synchronizacji tempa odtwarzania wykorzystano impulsy generowane na wyjściu SRate_Tick.

Plik musi znajdować się w katalogu głównym karty i musi mieć nazwę „#.WAV”, gdzie # = 0 … 9 w zależności od ustawienia SW(3:0). Sterowanie przełącznikiem obrotowym: RotL = start odtwarzania, RotR = przerwanie.

Diody LED wyświetlają parametry pliku, częstotliwość próbkowania wyświetlona jest na LCD.

Test_USB

[Sterownik LibUSB dla modułu USB_Function]

Wyświetlanie na ekranie VGA kodów ASCII otrzymywanych jako transmisja masowa USB plus zwracanie zanegowanego słowa 16b w odpowiedzi na transmisje kontrolne.

Przełącznik obrotowy steruje położeniem kursora na ekranie VGA wg połączeń jak na schemacie.

Projekt wymaga podłączenia poprzez kabel USB do komputera, na którym będzie uruchomiona aplikacja obsługująca transmisję do / z urządzenia USB_Function. Przykładowy kod źródłowy takiej aplikacji zawarty jest w pliku ZIP. Wykorzystuje on bibliotekę open–source LibUSB–Win32 (http://libusb-win32.sourceforge.net/, http://libusb.wiki.sourceforge.net/).

Podczas konfigurowania układu FPGA kabel USB powinien być odłączony. Po włożeniu kabla przy pierwszym wykryciu urządzania system Windows może poprosić o jego sterowniki, które także są w archiwum ZIP.

Test_DDR

Zapamiętanie ciągu 0-1 w pamięci DDR, następnie jego odczyt.

Jako wyświetlacz użyty jest monitor VGA: ruchy przełącznika obrotowego generują 0 (obrót w lewo) oraz 1 (obrót w prawo), wypełnienie całego wiersza na monitorze (48 znaków) rozpoczyna odczyt zapamiętanych wartości z pamięci DDR i wyświetlenie ich dla porównania w kolejnym wierszu.

Generowane zera i jedynki kopiowane są do najmłodszego bitu słowa zapisywanego w pamięci, pozostałe 31b jest niewykorzystanych.

Test_Accel

Wyświetlanie danych udostępnianych przez moduł AccelADXL345 na wyświetlaczu LCD: pierwsza linia zawiera odczytane przyspieszenia w kierunkach trzech osi, druga linia – licznik pomiarów. Słowo wczytywane z przełączników SW(3:0) jest używane podczas inicjalizacji do określenia częstotliwości pomiarów.

Test_Magneto

Wyświetlanie danych udostępnianych przez moduł MagnetoHMC5883L na wyświetlaczu LCD: pierwsza linia zawiera odczytane natężenia pola w kierunkach trzech osi, druga linia –licznik pomiarów. Słowo wczytywane z przełączników SW(2:0) jest używane podczas inicjalizacji do określenia częstotliwości pomiarów.

Test_OLED128x64

Przykład komunikacji ze sterownikiem SSD1306 wyświetlacza OLED 128x64. Projekt zawiera maszynę FSM, która (komunikując się poprzez sterownik I2C_Master) wykonuje automatycznie inicjalizację wyświetlacza, a następnie, gdy pojawia się impuls WriteByte = ‘1’, wysyła bajt z wejścia Byte jako maskę pikseli do wyświetlenia. Źródłem impulsów WrietByte jest na schemacie impulsator (RotaryEnc), natomiast bajt danych jest tworzony przez sklejenie stanu przełączników SW(3:0).

Realizowana w maszynie minimalna procedura inicjalizacji zresetowanego wyświetlacza polega na wysłaniu następującego strumienia bajtów w jednej transmisji wyjściowej I2C:

X"00", -- string prefix: commands (not

data) will follow

X"A1", X"C8", -- segment remap & reverse COM output

scan direction

-- (this will rotate

display upside-down; reset defaults: X"A0", X"C0")

X"20", X"00", -- set horizontal addressing mode

(different mode can be used,

-- if omitted -

default page mode will remain)

X"8D", X"14", -- enable charge pump

X"AF" -- turn display ON

Podstawowym źródłem pozostałych informacji o możliwościach wykorzystania wyświetlacza OLED jest dokumentacja jego sterownika SSD1306.

W projekcie zawarty jest też plik symulacyjny tbw_OLED_Ctrl.vhd, który jest testem jednostki z maszyną FSM: w wynikach symulacji można obejrzeć przykład, jak w tym konkretnym przypadku wygląda sterowania modułem I2C_Master.

Inne

projekty (pliki BIT)

PS2/Mouse > VGA

Test poprawnej pracy myszy: sterowanie krzyżowym kursorem na

ekranie VGA oraz wyświetlanie na LCD otrzymywanych komunikatów (jak w

Test_PS2Mouse).

Wymagana konfiguracja: mysz oraz

monitor VGA dołączone do płyty Spartan (Mouse2VGA_ExtBoard.bit - mysz dołączona

do dodatkowego portu PS/2 na płytce rozszerzającej).

ADC

> LCD

Wyświetlanie odczytów przetwornika ADC na LCD.

Pierwsza linia: wartości kanałów A i B w NKB (tylko 8 najstarszych bitów) oraz

w U2 (pełne 14b jak przekazane przez przetwornik).

Druga linia: aktualnie wysłane słowo konfigurujące przedwzmacniacz (zmiana

pokrętłem RotEnc).

Wymagana konfiguracja: dołączone

źródła sygnałów analogowych do gniazda J7 (np. potencjometry joysticka).

ADC

> VGA

Jak projekt ADC>LCD oraz dodatkowo wyświetlanie wartości

z kanałów A i B na wykresie X-Y na monitorze VGA.

Wymagana konfiguracja: dołączony monitor

VGA oraz źródła sygnałów analogowych do gniazda J7 (np. potencjometry

joysticka).

Termometr

1-Wire DS18S20

Komunikacja 1-Wire z cyfrowym termometrem DS18S20. Dwie

wersje:

HEX = wyświetlenie na LCD odczytanego wektora binarnego

ASCII = wyświetlenie wartości numerycznych.

Wymagana konfiguracja: dołączony do

gniazda J4 układ DS18S20.

PHY

Rx

Wyświetlanie bajtów odbieranych z portu Ethernet na

monitorze VGA (moduł PHY_Rx). Koniec pakietu

sygnalizowany przejściem do nowej linii, BTN_South =

Reset & ClrScr.

Wymagana konfiguracja: dołączony

kabel Ethernet oraz monitor VGA.

PHY

Tx

Wysyłanie ramki Ethernet (moduł PHY_Tx)

pod wpływem naciśnięcia klawisza klawiatury PS/2. Ramka składa się ze

standardowej preambuły 8B oraz kodu klawisza powtórzonego 24 razy. BTN_South = Reset.

Wymagana konfiguracja: dołączony

kabel Ethernet oraz klawiatura PS/2.

DDR

& VGA

Zapis różnych wzorów testowych w pamięci DDR, następnie

wyświetlanie ich na monitorze VGA. Na wyświetlaczu LCD pokazywany numer wzoru,

wybór innych pokrętłem RotEnc. Przyciśnięcie pokrętła

włącza automatyczne przełączanie wzorów. BTN_South =

Reset.

Wymagana konfiguracja: dołączony

monitor VGA.

Poziomnica

Wyświetlanie na monitorze VGA (tryb 800x600) znacznika

odchylonego od pozycji centralnej o wektor odczytany z wyprowadzeń X oraz Y

modułu AccelADXL345.

Przełączniki SW(3:0) dołączone

do wejścia DataRate

modułu, btn_south

= reset.

Wymagana konfiguracja: monitor

(złącze VGA), płyta GY-291 (złącze J4).

Kompas

Wyświetlanie na monitorze VGA (tryb 800x600) znaczników o

współrzędnych pobranych z wyprowadzeń DRX

oraz DRY modułu MagnetoHMC5883L. Przełączniki SW(2:0) dołączone do wejścia OutputRate

modułu, btn_south

= reset.

Wymagana konfiguracja: monitor

(złącze VGA), płyta GY-273 (złącze J4).

OLED128x64 – tryb auto horizontal scroll

Inicjalizacja wyświetlacza OLED, wysłanie kilku bajtów

danych z przykładową maską bitową oraz włączenie trybu automatycznego

przewijania w poziomie.

Wymagana konfiguracja: wyświetlacz

OLED128x64 (złącze J4).

Dodatki

Kody do symulacji

[Tbw_PS2Tx] – proces realizujący nadawanie bajtów na liniach magistrali PS/2. Do testowania odbiornika PS/2.

[Tbw_PS2Rx_DeviceClock] – proces generujący impulsy PS2_Clock, jakie podaje urządzenie podczas odbioru bajtu. Do testowania nadajnika PS/2.

[Tbw_RS232Tx] – proces realizujący nadawanie bajtu na linii RS_Rx (RS-232). Szybkość 115200, 1 bit stop, bez parzystości. Do testowania odbiornika portu szeregowego.

[Tbw_1Wire_PresencePulse] – proces generujący tzw. presence pulse jako odpowiedź urządzenia na komendę reset. Do testowania kontrolera magistrali 1-Wire.

[Tbw_SDCFileReader] – proces imitujący pracę modułu SDC_FileReader. Do testowania modułów odczytujących pliki z karty SDC.

[Tbw_I2Cslave] – proces symulujący pracę urządzenia dołączonego do magistrali I2C: w oknie konsoli symulatora drukuje komunikaty opisujące zdarzenia (start/stop condition, odebrane bajty) oraz generuje odpowiedzi na linii SDA (ACK, nadawanie kolejnych bajtów w transmisjach WE). Do testowania projektów używających magistralę I2C, także poprzez moduł I2C_Master.

[Test_VGAscan] – uniwersalna jednostka VGAscan, która w czasie symulacji monitoruje port VGA i wyświetlane na nim obrazy zapisuje w formacie BMP. Plik zawiera kompletny projekt ISE, w którym jednostka jest użyta do przechwytywania obrazów wyświetlanych przez moduł VGAtxt48x20 (zob. symulację Tbw_VGAscan). Dostępna w wersjach generujących obrazy 3bpp (8 kolorów, jak na płycie Starter Board) oraz 24bpp (pełne kolory).

Oryginalne

pliki konfiguracyjne płyty

Aby przywrócić fabryczną konfigurację testową płyty należy zaprogramować pamięć szeregową oraz układ CPLD (wykrywane w łańcuchu JTAG) plikami z podanego archiwum.